| Locus originis: | Zhejiang |

| Nomen marcae: | Inventchip Technologia |

| Numerus modeli: | IVCR1402DPQR |

| Certificatio: | AEC-Q100 qualificata |

1. Caracteres

• Capacitas motoris: 4A immissio et emissio culmine correntis

• Latus VCC ambitus usque ad 35V

• Integrata 3.5V negativa praejudicium

• Concepta pro parte inferior et apta pro bootstrap alta laterali potestate

• UVLO pro positiva et negativa motiva voltage

• Desaturation detectio pro protectione brevis circuiti cum interna tempore praebitionis

• Output culpae cum UVLO aut DESAT deprehensus

• Referentia 5V 10mA pro circuitu externo, e.g. isolator digitalis

• Ingressus congruens TTL et CMOS

• SOIC-8 cum pad aperto pro applicationibus altae frequentiae et potentiae

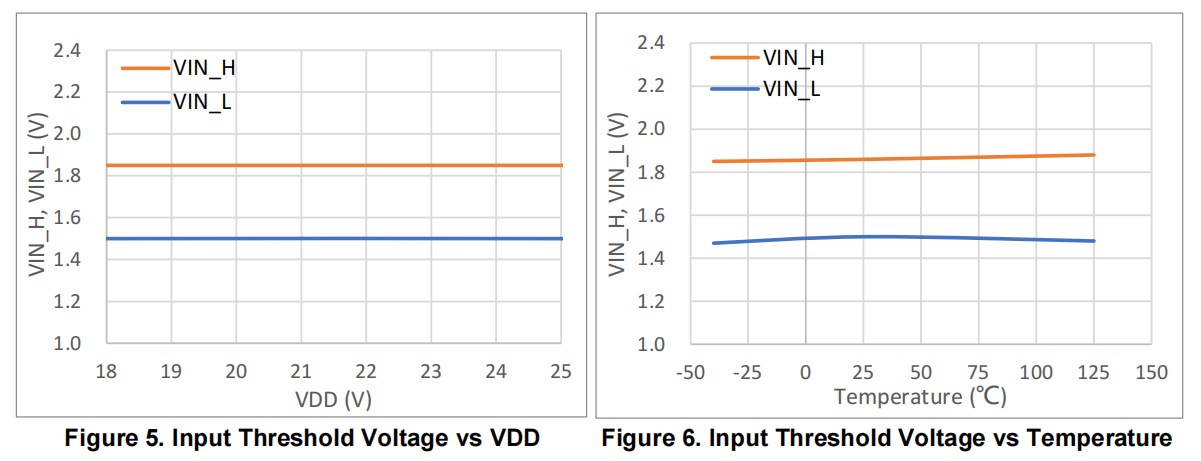

• Parva mora propagationis 45ns typica cum filtro de-glitch integrato

• Qualificatus AEC-Q100

2. Applicationes

• EV On Board Recipientes

• EV/HEV inversores et stationes charging

• AC/DC et DC/DC conversores

• Motorius Impulsor

3. Descriptio

IVCR1402Q est AEC-Q100 qualificatus, 4A unius canalis, velox intelligens driver, qui potest efficienter et secure SiC MOSFETs et IGBTs agitare. Fortis impetus cum praeiudicio negativo meliorem immunitatem adversus effectum Miller in operatione alta dv/dt praebet. Desaturationis delectio firmam protectionem contra breve circuitum et periculum damni componentium systematis et dispositivorum minuit. Insertus tempus blanking fixum 200ns praeservat overcurrent protection a praematura activatione per spiculum et rumor currentis commutationis. Fixa positiva gate drive voltage UVLO et fixa negativa praeiudicium UVLO protection voltages portae salubres operari facit. Signum culpae activum bassum systemam notificat quando UVLO aut super currus accidit. Parva propagatio morae et mismatch cum exposto thermico pad habilitat SiC MOSFETs ad commutationem in centenis kHz. Integrata generatio voltatis negativae et output referentia 5V minimum numerum componentium externarum minuit. Est primus industrialis SiC MOSFET et IGBT driver qui includit generationem voltatis negativae, desaturationem et UVLO in package octo-pin. Ideale driver est pro design compacto.

Informatio de Dispositivo

| PARTNUMBER | Sarcina | Sarcina | ||||||||||||||||||

| IVCR1402DPQR | SOIC-8 (EP) | Tape et Reel | ||||||||||||||||||

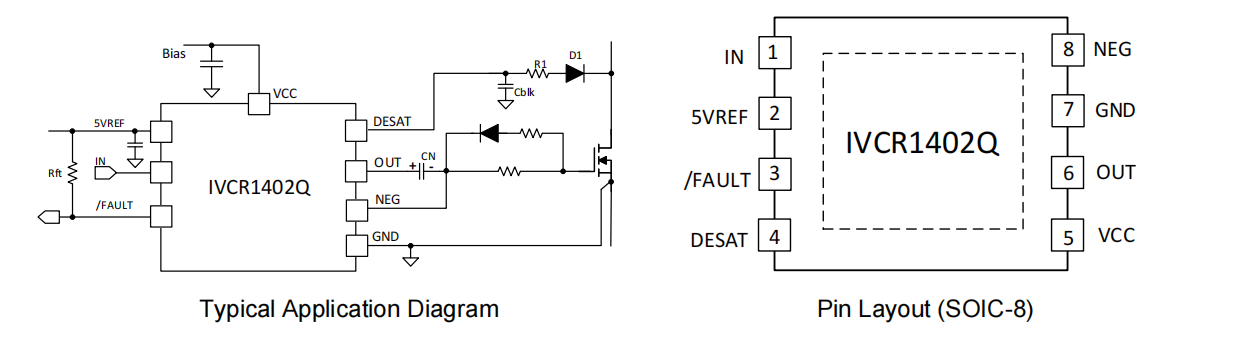

4. Configuratio et Functiones Pinnarum

| Pinna | Nomen | Ption3: Cu | Descriptio | |||||||||||||||||||||||||||||||||||||||||

| 1 | In | I | Input logicum | |||||||||||||||||||||||||||||||||||||||||

| 2 | 5VREF | O | 5V/10mA exitus pro circuito externo | |||||||||||||||||||||||||||||||||||||||||

| 3 | /FAULT | O | Exitus collectoris aperti, trahitur ad inferius quando superat amperitatem aut UVLO deprehenditur. | |||||||||||||||||||||||||||||||||||||||||

| 4 | DESAT | I | Input detegendi desaturationem | |||||||||||||||||||||||||||||||||||||||||

| 5 | VCC | P | Positiva praesidium suppeditatio | |||||||||||||||||||||||||||||||||||||||||

| 6 | Out | O | Porta motoris exitus | |||||||||||||||||||||||||||||||||||||||||

| 7 | GND | G | Motoris terra | |||||||||||||||||||||||||||||||||||||||||

| 8 | NEG | O | Negativa voltus exitus | |||||||||||||||||||||||||||||||||||||||||

| Patefacta calculus | Inferior patefacta calculus saepe coniungitur ad GND in dispositione. | |||||||||||||||||||||||||||||||||||||||||||

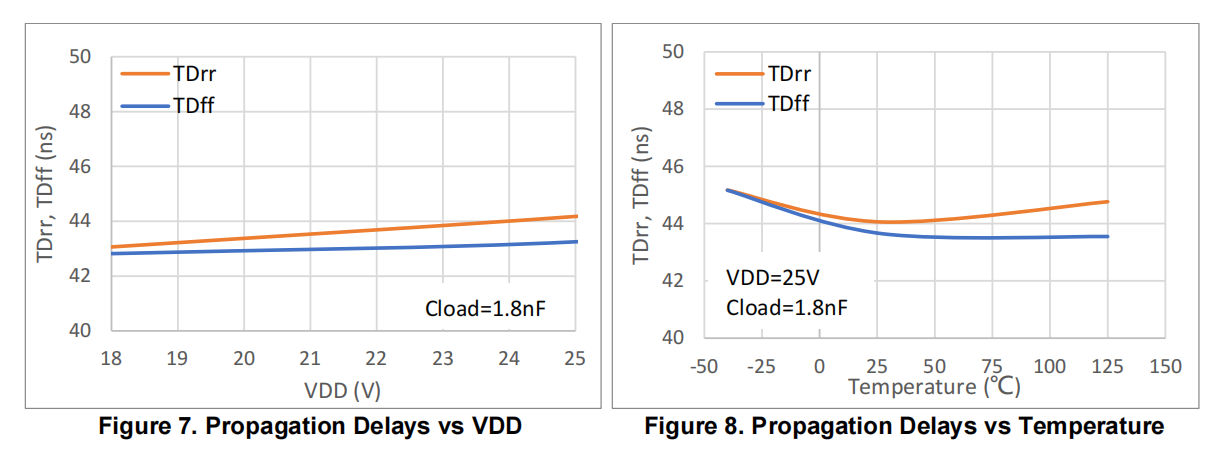

5. Specificaciones

5.1 Absolutae Maxime Censurae

Super liberum aerem temperatura ambitum (nisi aliter notatum) (1)

| Min max | Unitas | ||||||||||||||||||||||||||||||||||||||||||

| Tota tensio praebendi VCC (referentia ad GND) | -0.3 35 | V | |||||||||||||||||||||||||||||||||||||||||

| VOUT Tensio exitus motoris portae | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| IOUTH Exitus motoris portae cursus fontis (ad maximam latitudinem impulsi 10us et cyclo officii 0.2%) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| IOUTL Exitus motoris portae cursus amussim (ad maximam latitudinem impulsi 10us et cyclo officii 0.2%) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| VIN Tensio signi IN | -5.0 20 | V | |||||||||||||||||||||||||||||||||||||||||

| I5VREF Cursus exitus 5VREF | 25 | ma | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Tensio ad DESAT | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| Tensio VNEG ad pinum NEG | OUT-5.0 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| Temperatura Junctionis TJ | -40 150 | °C | |||||||||||||||||||||||||||||||||||||||||

| Temperatura Storagii TSTG | -65 150 | °C | |||||||||||||||||||||||||||||||||||||||||

(1) Operatio ultra ea quae sub Cotationibus Maxime Absolutis enumerantur possit damnum perpetuum instrumento inferre.

Expositio ad conditiones maxime absolutas per tempus longum reliabilitatem instrumenti possit affectare.

5.2 Cotatio ESD

| Valor | Unitas | |||||||||||||||||||||||||||||||||||||||||||

| V(ESD) Discharge Electrica Statica | Modello corporis humani (HBM), secundum AEC Q100-002 | +/-2000 | V | |||||||||||||||||||||||||||||||||||||||||

| Modello apparatus incussi (CDM), secundum AEC Q100-011 | +/-500 | |||||||||||||||||||||||||||||||||||||||||||

5.3 Operationis Conditiones Recommandatae

| Min | MAX | Unitas | ||||||||||||||||||||||||||||||||||||||||||

| Tota tensio praebendi VCC (referentia ad GND) | 15 | 25 | V | |||||||||||||||||||||||||||||||||||||||||

| VIN Voltas input | 0 | 15 | V | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Tensio ad DESAT | 0 | VCC | V | |||||||||||||||||||||||||||||||||||||||||

| TAMB Temperatura ambientis | -40 | 125 | °C | |||||||||||||||||||||||||||||||||||||||||

5.4 Informatio Thermica

| IVCR1402DPQR | Unitas | ||||||||||||||||||||||||||||||||||||||||||

| RθJA Ad iuncturam ab Ambiente | 39 | °C\/W | |||||||||||||||||||||||||||||||||||||||||

| RθJB Ad iuncturam ad PCB | 11 | °C\/W | |||||||||||||||||||||||||||||||||||||||||

| Iunctio ad padam expositam | 5.1 | °C\/W | |||||||||||||||||||||||||||||||||||||||||

5.5 Specificatio Electrica

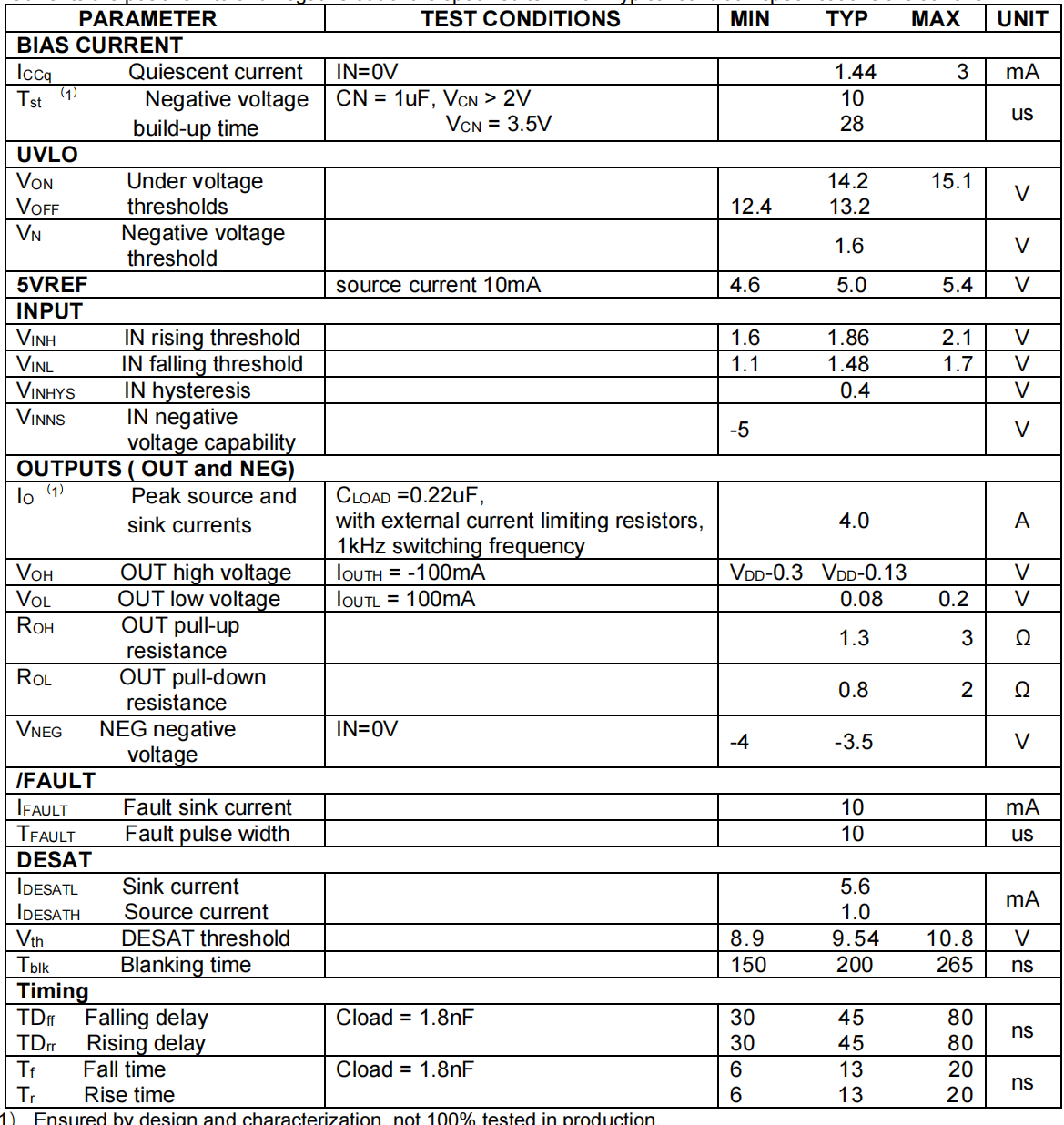

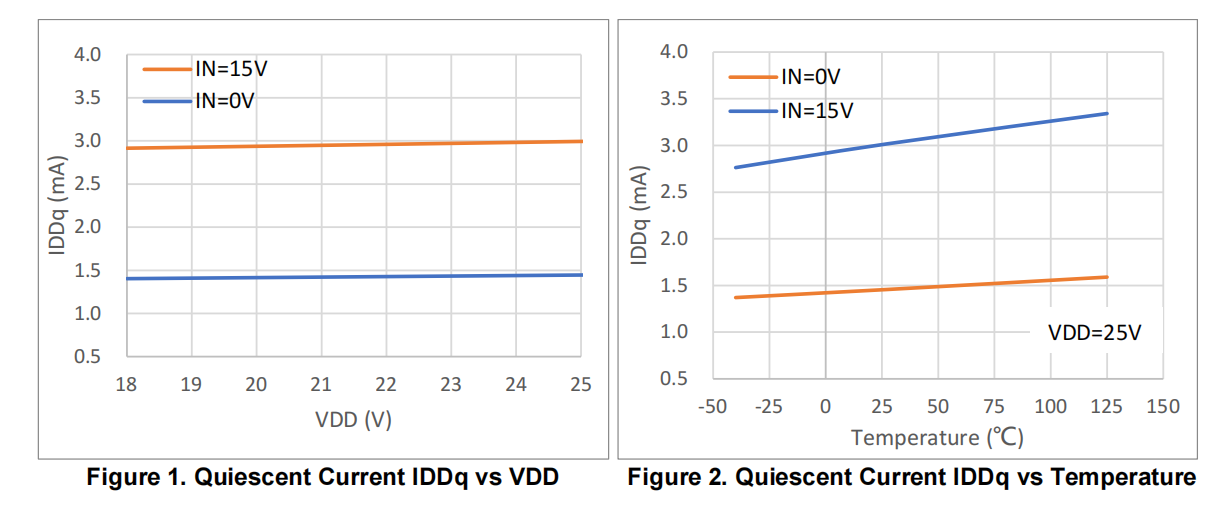

Nisi aliter notatum, VCC = 25 V, TA = –40°C usque 125°C, capacitatem bypass 1-μF a VCC ad GND, f = 100 kHz.

Currentes sunt positivi in et negativi ex termino specificato. Specificatio conditionum typicarum est ad 25°C.

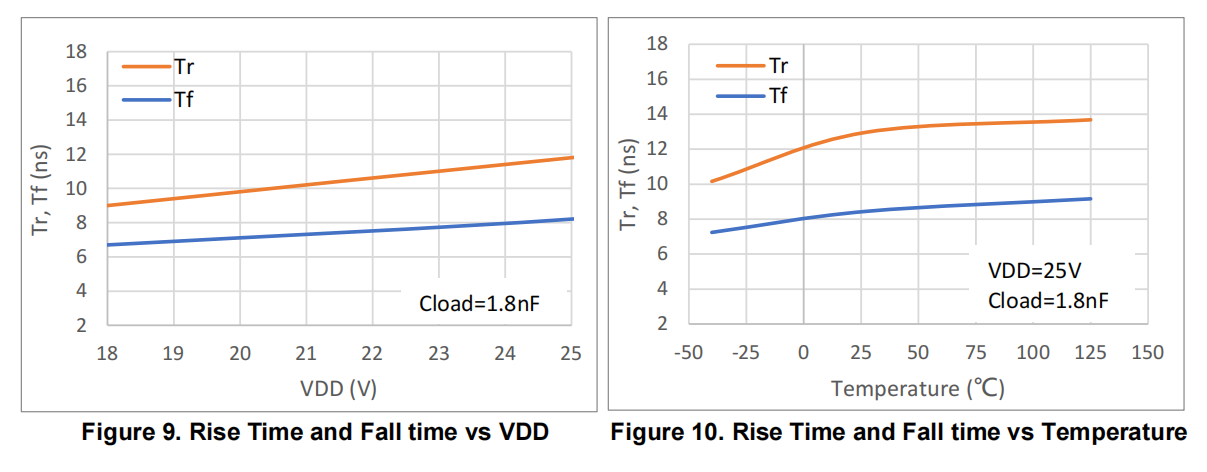

6 Caracteristica Typica

7 Descriptio Detail

IVCR1402Q driver repraesentat technologiam praecipuam singularis canalis lateris inferioris celeris portae driver ab InventChip

cum generatione negativa voltagii inserta, protectione desaturationis/connexionis brevis circuitus,

programmabili UVLO. Hic driver offert caracteristicas optime in classe et compactissimas ac fidissimas

Controllem portae SiC MOSFET. Est primus driver industriae instructus omnibus necessariis portae SiC MOSFET

characteristicae conducentis in congeries SOIC-8.

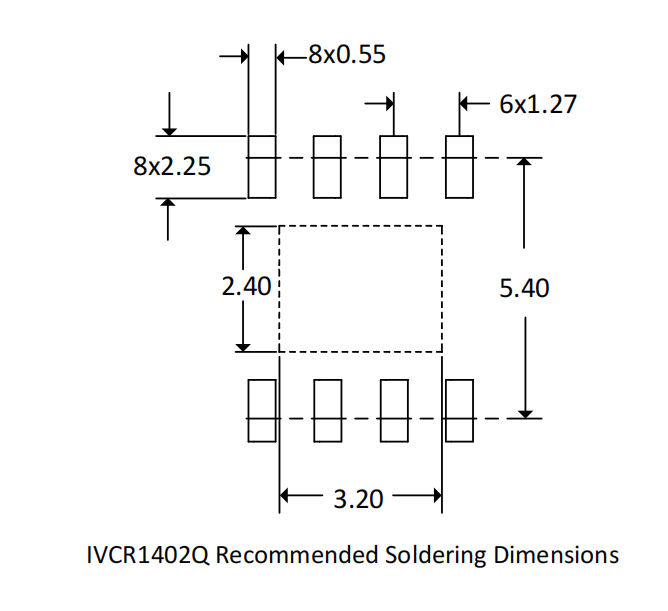

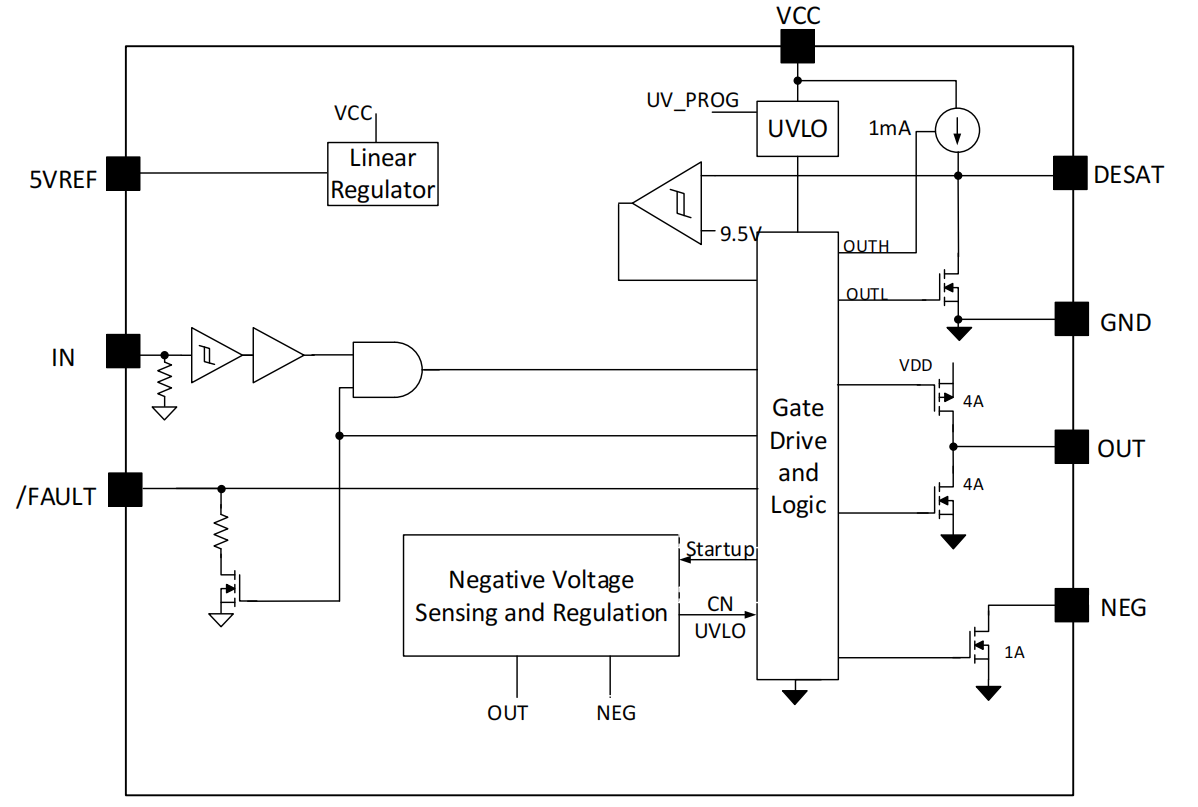

Diagramma Segmenti Functionalis

7.1 Ingressus

INGRESSUS est ingressus non inversorius portae logicae. Pinus habet levem trahentem ad terram. Ingressus est niveau logicae TTL et CMOS

compatibilis cum maxima tolerantia ingressus 20V.

7.2 Egressus

IVCR1402Q praebet stadium egressus cum 4A totem-pole. Praestat altum summitatem fontis currentis quando necessarium est durante regione plateau Miller transitionis incendi commutatoris potentiae. Fortis capacitas siccandi resultat in

nimium parvam impeditatem trahentis in stadio egressus qui meliorat immunitem adversus effectum parasitico Miller

incendionis, praesertim ubi MOSFETs Si cum parva capita porta aut emergentes latae bandae SiC MOSFETs sunt

utilizati

usus.

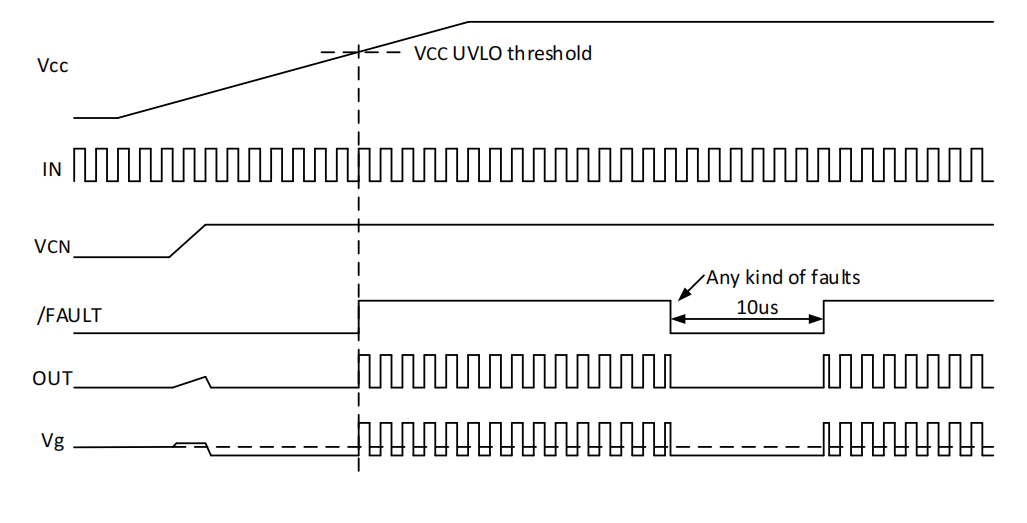

7.3 Generatio Voltaminis Negativi

In initio, NEG exitus trahitur ad GND et praebet viam magnae intensitatis pro fonte intensitatis ad capaciatorem negativum externum CN (1uF typicum) per pin OUT. Capacitor potest ad superius

2.0V in minus quam 10us incipiendi tempore compleri. Antequam voltasim capacitoris, VCN, compleatur, /FAULT manet bassa/activa, non respiciens logicum gradum IN. Postquam praejudicium negativum paratum est, tam NEG pin quam /FAULT pin liberantur et OUT incipit

sequi signum input IN. Internus regulator voltaminis negativi regulat voltaminem ad -3.5V pro operatione normali, sine respectu ad frequentiam PWM et cyclus officii. Signum impulsionis portae, NEG, tunc commutat inter

VCC-3.5V et -3.5V.

operationem, absque ratione frequentiae PWM et cycli officii. Signum impulsus portae, NEG, tunc commutat inter

vCC-3.5V et -3.5V.

VCC-3.5V et -3.5V.

7.4 Protectiones Sub-Voltaminis

Omnes praeiudicia interna et externa motoris sunt monitae ut salubris status operationis conservetur. VCC est

monita ab circuitu detegentis subvoltae. Exitus motoris claudetur (trahitur ad imum) vel permanet in imo si

voltae est infra finem praefixum. Notandum est quod limen VCC UVLO est 3.5V maius quam voltae portae.

Voltae negativae insuper monitae sunt. Limen eius UVLO habet fixam voltaginem negativam 1.6V. Defectus

capacitoris voltaginis negativae potest facere ut volta capacitoris sit infra limen. Protectio UVLO deinde

Tractabit portam MOSFET ad terram. \/FAULT trahitur ad imum cum UVLO deprehenditur.

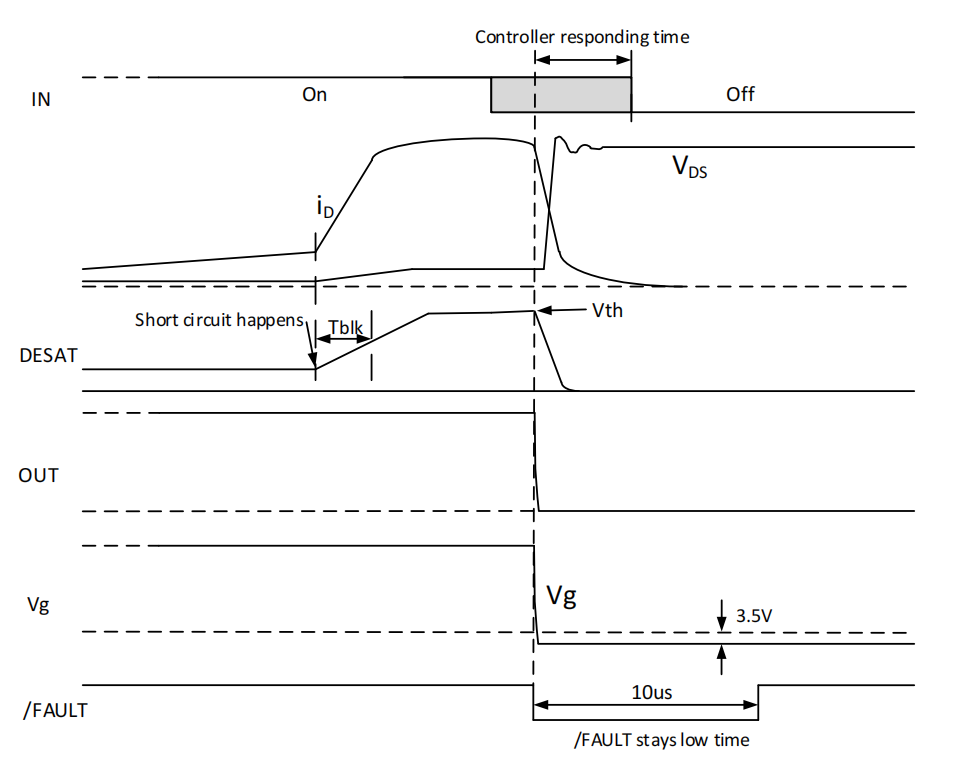

7.5 Detectio Desaturationis

Cum breve circuius aut supercurrus accidit, currus apparatus potentis (SiC MOSFET aut IGBT) a dreno aut collectore

potest crescere ad tantum magnae valorem ut apparata ex statu saturations exeant, et Vds\/Vce apparatorum

ascendet ad valorem multum magnum. Pin DESAT cum capacitore blanking Cblk, saepius alligatus ad

Id x Rds_on, nunc potest ad multo maius incipiens a fonte interna constantis 1mA. Cum tensus est

voltaeous usque ad typicum 9.5V limen, OUT et \/FAULT ambo trahuntur infimus. Tempus initiale 200ns insertum est

ad OUT ascendens marginem ut praeveniat circuitum protectionis DESAT ab initio praecipitari propter descensum Coss.

Ut minimum sit amissio fontis interni constantis, fontis constans extinctus est quando principalis commutator

est in statu off. Per electionem capacitatis diversae, tempus morae extinctionis (externum tempus initiale) potest esse

programmata. Tempus initiale computari potest cum

Teblk = Cblk ∙Vth ∕ IDESAT

Per exempli gratia, si Cblk est 47pF, Teblk = 47pF ∙9.5V ∕ 1mA = 446ns.

Notandum est quod Teblk includit iam tempus internum Tblk 200ns.

Pro limite currentis configuratione, sequens aequatio adhiberi potest,

Ilimit = (Vth – R1* IDESAT – VF_D1)\/ Rds_on

ubi R1 est resistor programmaticus, VF_D1 est directio voltii diodi alti voltii, Rds_on est conversio ad temperaturam junctionis aestimatae, sicut 175C.

resistentia in SiC MOSFET turn

Systema potentiae aliud saepe tempus conversionis aliud requirit. Optimum tempus conversionis potest maximam capacitatem brevis circuitus systematis maximam facere

dum Vds et voltium bustae resonantiam limitat.

7.6 Fault

\/FAULT est exitus collectorem apertum sine resistencia pull-up interna. Cum desaturationes et voltii inferiores

sunt deprehensae, pin \/FAULT et OUT ambo trahuntur ad imum. Signum \/FAULT permanebit ad imum per 10us postquam

conditio fault est remota. \/FAULT est signum auto recuperationis. Controller systematis decernere debet quomodo

respondere signo \/FAULT. Sequens diagramma ostendit ordinem signorum.

7.7 NEG

Capacitor externus bias negativus cito incipit ad summam cum NEG descendit. Hoc evenit dum potentia surgit

et tempus reinitii, iusto antequam 10us periodus /FAULT low expirat post quamlibet culpam detectam. Dum potentia surgit

et tempus reinitii, voltas capacitoris bias negativi VCN metiturur. Statim postquam voltas praeter VN

Limitem UVLO transit, NEG fit alta-impedantia et OUT recipit dominium super controllo portae.

8 Applicationes et Implementatio

IVCR1402Q est driver idealis pro design compacto. Est driver lateris inferioris. Tamen, cum generator intus positus

voltatis negativae, driver potest uti velut driver lateris superioris sine usus bias segregatus.

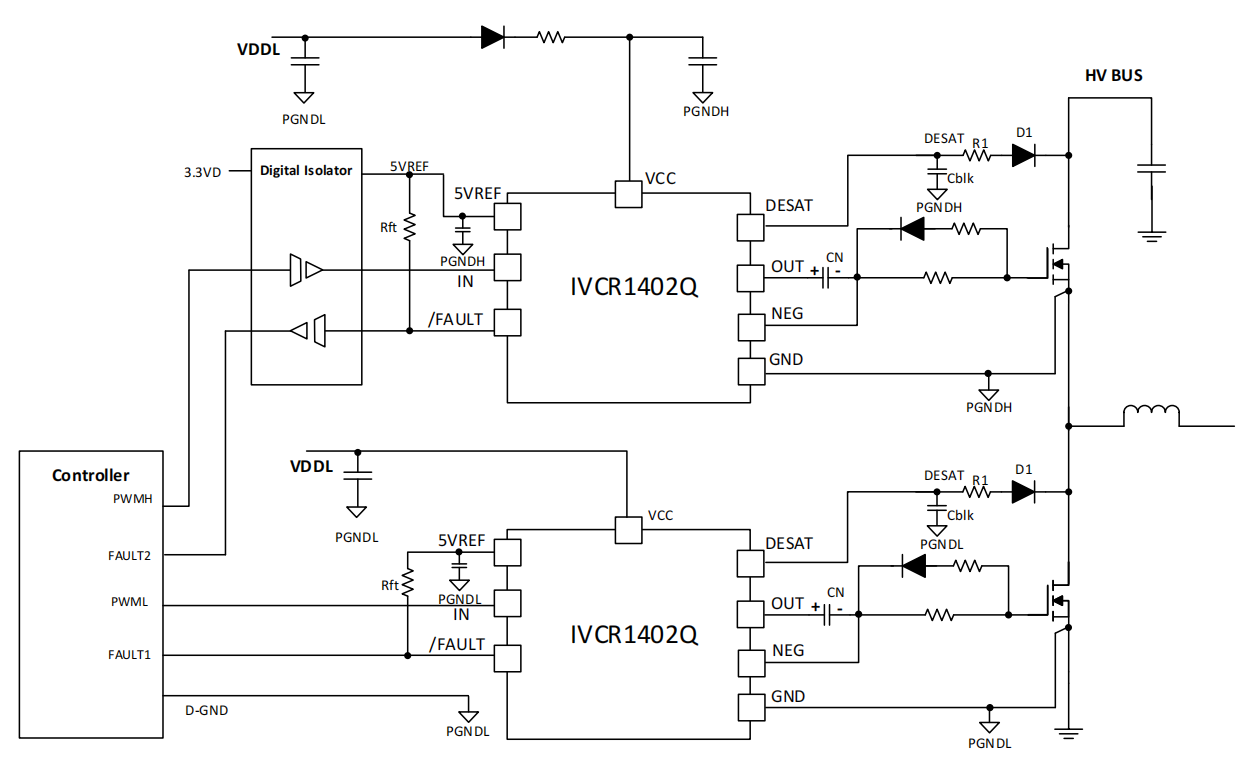

Tunc potest bootstrap parvum-costum uti pro loco. Diagramma circuitus sequens monstrat applicationem typicam pontis semis

driver.

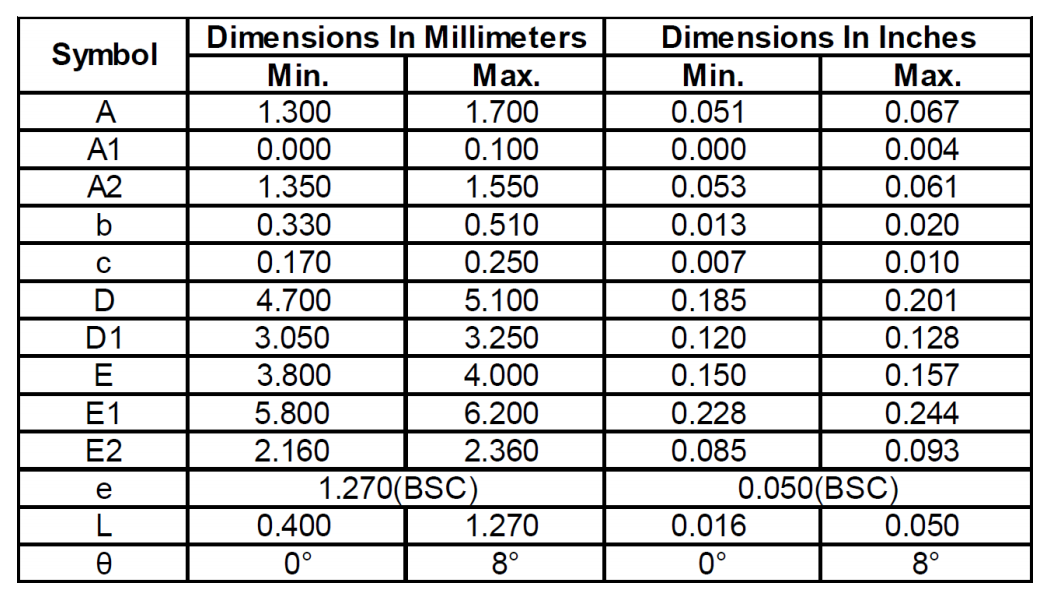

9 Dispositio

Bonus planus est gradus clavis ad desideratum circuitum operationem consequendum. Solidus tellus est primus ut cum initiare.

Commendatur ut pad apertum ad driver tellus alligetur. Regula generalis est quod capacitores habent

prioritatem maiorem quam resistores pro loco arrangemente. Capacitor 1uF et capacitor decoupling 0.1uF

prope ad VCC pin esse debent et ad driver tellus planum coniuncti. Capacitor negativae voltus prope

ad OUT et NEG pins collocari debet. Capacitor blanking prope ad driver esse debet quoque. Parvus filter

(cum constante temporis 10ns) forte necessarius erit ad inputum IN si input signal traces pertransire debeant

per aliquam regionem noisy. Sequens est dispositio commendata.

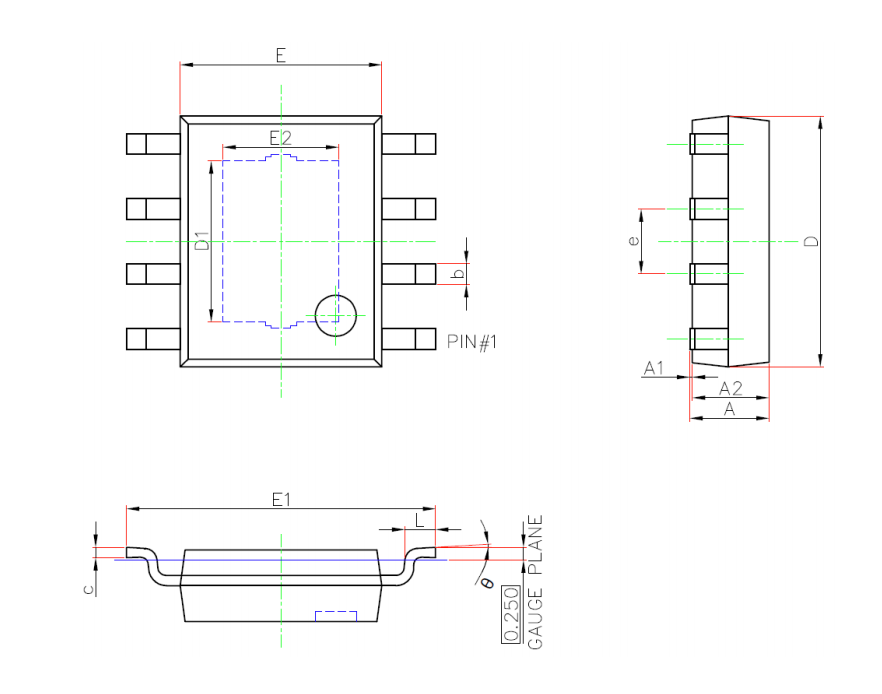

10 Informationes de Packaginis

SOIC-8 (EP) Dimensiones Packaginis